The Do's and Don'ts of Signal Routing for Controlled Impedance p.18

Impedance Control, Revisited p.24

an I·Connect007 publication

**CONTROLLED IMPEDANCE**

# PCB BUYERScompare nearly 1900 manufacturers now at *The* PCB List.

Quick Search

Advanced Search

The best way to find a PCB fabricator, anywhere.

# HIGH-SPEED PCB DESIGN TRAING

- One-on-one mentoring

- Develop your skills with confidence

- Ensure your next design performs reliably

# **FEATURED CONTENT**

Controlled impedance PCBs are becoming more common now, especially in high-speed applications. Designing these boards can be particularly challenging. This month our expert contributors Barry Olney of In-Circuit Design, Martyn Gaudion of Polar Instruments, and Mark Thompson of Prototron Circuits focus on the ins and outs of controlled impedance design.

# **10 Controlled Impedance Design** by Barry Olney

# 18 The Do's and Don'ts of Signal Routing for Controlled Impedance

by Mark Thompson

**24** Impedance Control, Revisited by Martyn Gaudion

# RF/Microwave Materials & Resources

- ► IS680 materials offers a complete laminate materials solution for single- and double-sided printed circuit designs and is a cost-effective alternative to PTFE and other commercial microwave materials.

- ► I-Tera® MT RF materials are available in 0.010", 0.020" and 0.030" in 3.38, 3.45 and 3.56 Dk.

- ▶ I-Tera® MT materials are suitable for both high-speed digital and RF/ microwave designs. A full compliment of cores and prepregs allowing flexibility in design is available in core thicknesses from 0.002" to 0.018".

- ► TerraGreen® halogen-free, very low-loss, thermoset materials are available in a variety of laminate and prepreg offerings. This material is inexpensive to process – improving your company's bottom line, as well as the environment.

- The revolutionary Astra® MT ultra low-loss thermoset laminates are a replacement for PTFE. These materials have been used for hybrid applications with Isola's 185HR and 370HR products.

|                                                         | RF/MICROWAVE MATERIALS                   |                            |                 |                 |                 |  |  |  |  |

|---------------------------------------------------------|------------------------------------------|----------------------------|-----------------|-----------------|-----------------|--|--|--|--|

|                                                         | IS680                                    | I-Tera® MT RF              | I-Tera® MT      | TerraGreen®     | Astra® MT       |  |  |  |  |

| Tg                                                      | 200°C                                    | 200°C                      | 200°C           | 200°C           | 200°C           |  |  |  |  |

| Td                                                      | 360°C                                    | 360°C                      | 360°C           | 390°C           | 360°C           |  |  |  |  |

| Dk @ 10 GHz                                             | 2.80 - 3.45                              | 3.38, 3.45 & 3.56          | 3.45*           | 3.45*           | 3.00            |  |  |  |  |

| Df @ 10 GHz                                             | 0.0028 - 0.0036                          | 0.0028, 0.0031 &<br>0.0034 | 0.0031*         | 0.0030*         | 0.0017          |  |  |  |  |

| CTE Z-axis (50 to 260°C)                                | 2.90%                                    | 2.80%                      | 2.80%           | 2.90%           | 2.90%           |  |  |  |  |

| T-260 & T-288                                           | >60                                      | >60                        | >60             | >60             | >60             |  |  |  |  |

| Halogen free                                            | No                                       | No                         | No              | Yes             | No              |  |  |  |  |

| VLP-2 (2 micron Rz copper)                              | Available                                | Available                  | Available       | Standard        | Standard        |  |  |  |  |

| Stable Dk & Df over the temperature range               | -55°C to +125°C                          | -55°C to +125°C            | -55°C to +125°C | -55°C to +125°C | -40°C to +140°C |  |  |  |  |

| Optimized global constructions for Pb-free assembly     | Yes                                      | Yes                        | Yes             | Yes             | Yes             |  |  |  |  |

| Compatible with other Isola products for hybrid designs | For use in double-<br>sided applications | Yes                        | Yes             | Yes             | Yes             |  |  |  |  |

| Low PIM < -155 dBc                                      | Yes                                      | Yes                        | Yes             | Yes             | Yes             |  |  |  |  |

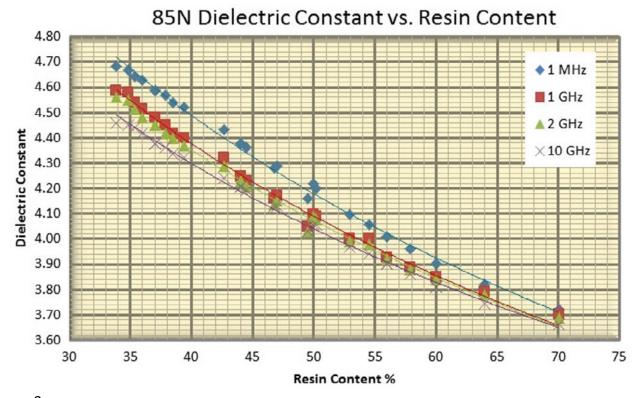

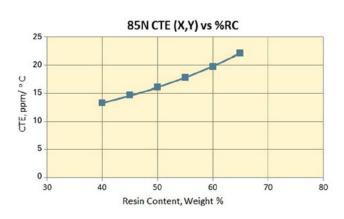

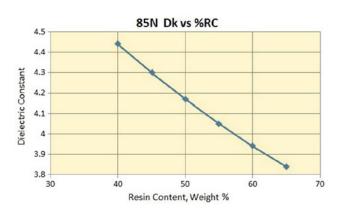

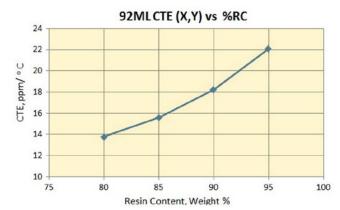

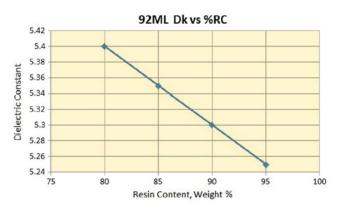

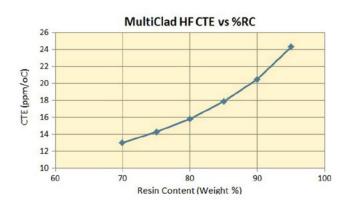

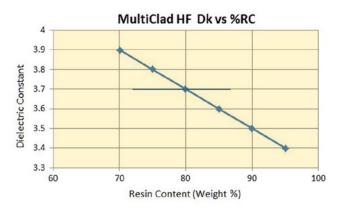

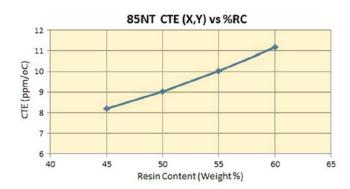

# \* Dk & Df are dependent on resin content NOTE: Dk/Df is at one resin %. Please refer to the Isola website for a complete list of Dk/Df values. The data, while believed to be accurate & based on analytical methods considered to be reliable, is for information purposes only. Any sales of these products will be governed by the terms & conditions of the agreement under which they are sold.

### **RF Conversion Service**

- Isola's Design Review Service can facilitate your conversion to Isola's RF/microwave products and get you to market faster with the newest, ultra-low-loss materials.

- As part of this new service, Isola's technical staff will provide turn-key calculations, testing, characterizations and material recommendations to assist PCB fabricators and OEMs in converting to Isola's RF-materials, which will help overcome the current material shortages of other vendors and accelerate time-to-market. The design review service will also address the perceived conversion issues when migrating from a currently used material to an Isola material.

http://www.isola-group.com/conversion-service

### **FREE! Impedance and Power-Handling Calculator**

- Isola's free Impedance and Power-Handling Calculator predicts the design attributes for microstrips and striplines based on the design's target impedance and dielectric properties of the company's RF, microwave and millimeter-wave laminate materials.

- This software tool provides a design or an equivalent dielectric constant to facilitate modeling for PCB designers to predict impedance and other design attributes. The software computes changes in the effective dielectric constant due to dispersion at higher frequencies. The software then computes the total insertion loss a measure of power lost through heat for power handling calculations, including the dielectric loss, conductor loss, and the loss due to the surface roughness. The main factors affecting the typical power-handling capability of a material are its thermal conductivity, the maximum operating temperature, and the total insertion loss.

https://isodesign.isola-group.com/phi-calculator

NUMBER 5

MAGAZINE thepcbdesignmagazine.com

THE OPTIMUM

**MAGAZINE**

**DEDICATED TO**

**PCB DESIGN**

an I-Connect007 publication

# CONTENTS

48 The Composite **Properties of** Rigid vs. **Multilayer PCBs**

by Chet Guiles

**60** Electronic Design Training Crucial to Industry Growth

by Bob Sadowski

**COLUMNS**

8 The Readers Speak by Andy Shaughnessy

## **VIDEO INTERVIEW**

57 Solution for High-Temperature **Applications**

### **SHORTS**

- 22 New Stream for Topological **Quantum Computer Research**

- 29 Novel Nanotube Tunnel FET Architecture

- 47 Sodium-ion Hybrid Capacitor as **Next-generation Battery**

- 63 Putting a New Spin on Plasmonics

- HIGHLIGHTS

- 30 PCB007

- 58 Mil/Aero007

- 64 PCBDesign007

### **EXTRAS**

- **66 Events Calendar**

- **67** Advertiser Index & Masthead

# **Engineering And Providing Balanced Interconnect Solutions**

# Flexible Printed Circuits • Rigid Flex • Wire Harnesses • Complete Assemblies

Our products and services are specifically designed to empower our customers to produce a product with superior performance and quality, as well as lower design, assembly, and system installation costs.

Partnering With Your Engineering Team To Deliver The Best Solution

...connecting technology

### THE SHAUGHNESSY REPORT

# The Readers Speak

# by Andy Shaughnessy

I-CONNECT007

I wish I could read minds. If I could, I'd know exactly what sort of problems you all face when you're designing PCBs, what sort of technology you're working with, and what sort of trends you're seeing in PCB design and PCB manufacturing.

But since I'm not clairvoyant, I have to resort to other means to find out about our readers' trials and tribulations. This is where our reader surveys come in. The survey is one of the best ways for us to find out about you and your job, which helps us to be certain that we're providing you the most relevant content possible.

Best of all, surveys give the reader a voice. What's on your mind? We really want to know.

Recently, we sent out a survey with a handful of questions; we've found that surveys with too many questions don't get answered. One question was, "Does supply chain management affect your job?"

The answers were surprising. Almost 2/3 of you said no, the supply chain doesn't affect your job in any meaningful way. But a third of you said the exact opposite: The supply chain impacts your job directly, and for some of you, it's a big problem.

A very vocal minority left us a variety of great comments regarding their supply chain challenges. Here is a sample of the comments for that question:

- New parts availability and older parts going obsolete.

- Availability of parts.

- Component/part selection.

- The part selection process at the front end of the design.

- Component availability and end of life.

Medical products could have a 15-year life.

- Replacing old parts, verifying parts are active and available.

- Cost factor and similar vendor capability for second source.

- Design updates after the board is complete

due to part limitations.

- Having to correct layout due to changed components.

- Orders for parts affected by proposed ECOs have to be factored in, as procurement has outstanding orders for not only parts affected, but parts that may be affected by the ECO.

- Didn't used to, but as we go to higher frequencies into the millimeter wave range (like 60-86 GHz), the material choices, component choices, and fabricator choices decrease. We are having to source and stock material ourselves.

- Company changes CM from proto to production. Sloppy production at best.

- Cannot predict board and component suppliers in certain projects.

- Late changes to component selection due to too long delivery.

- Too much bureaucracy! Too many hands in the pie! Singular POC personnel for many tasks is WAY TOO MUCH!

You designers in the minority are serious about this. But why did the majority of respondents say that the supply chain had no effect on their job? I imagine it depends upon your employer; do some OEMs have a foolproof system for managing the supply chain?

I can't help wondering why there's such a huge dichotomy here, with most respondents saying, "No problems with the supply chain here," while a third of you are having a tough time ensuring that the necessary components, parts, and materials are available for your designs. What do you think—is the supply chain a problem for you? Let me know what you think.

We also asked, "When designing a PCB, what are your greatest challenges?" Here are some of the best comments for that question:

Getting correct and complete information from the engineers.

### THE READERS SPEAK continues

- Engineering, and getting the circuit completed and final on a timely basis.

- Engineers.

- Getting a complete schematic/rules.

- Receiving PCB requirements when starting a design.

- Bugs in the software.

- The bad design tool.

- The density and small pitch of the BGA components.

- Keeping the hole-to-copper clearance, especially when routing diff pairs within a BGA area.

- Getting out of large BGAs without the use of HDI.

- Maximizing the most out of the available

- Getting it all to fit and be routable and DFM in the board size.

- Board size vs, density.

- Space for components and space for tracking.

- To fit everything in the board space.

- Fitting everything into small areas and keeping costs low.

- Fitting small component packages elegantly on large transmission lines.

- Meeting deadlines.

- Time. (3x)

- Time to market.

- Meeting schedules.

- Stackup design.

- Impedance control.

- Signal integrity.

- Getting paid.

- Customer stupidity.

We see some definite trends here. Communication with engineers seems to be a constant complaint among designers, and that's reflected here. Do any of you have a great working relationship with your engineers? It may be just an interdisciplinary difference in working styles, but there's certainly a disconnect between designers and engineers.

The lack of time and shrinking board space are other repeat answers. I'm not sure that there's a fix for these problems; time-to-market and board space are always decreasing. Then there's the bad EDA tool, another constant refrain from designers. And you have to love the last answer, "customer stupidity."

Finally, we asked, "What is the most important thing you have learned on the job in the past year?" Here are some of the more interesting comments:

- To reduce my hourly rate by a factor of 3 and multiply my reported work hours by a factor of 5.

- That I could have made a lot more money with a business/management degree!

- Communication is critical no matter where vou are located.

- Take more time to evaluate parallel designs done by outside vendors before setting design schedule.

- Workarounds for lousy PCB software.

- There are many "experts" on CAD layout who want to help me.

- Not to design on the edge of technology.

- Good time estimation for different kind of projects.

- More people involved means more delays and more chaos.

- That all PCB vendors are not honest.

- Allegro PCB Editor is a real mother to learn how to use.

- Allow more time for the mechanical designer to finished his part of the design.

- How to handle DDR3 implementation.

- Cost is not king.

- Breaking out .5 mm BGAs.

- Nothing.

As always, we appreciate the input from everyone who responded to this survey. You can be sure that we'll be pinging you again in the future. These surveys help us stay informed about the challenges you face, and they also provide you with a soapbox. If you want to make your voice heard, answer one of our surveys. We just might post your comments. PCBDESIGN

Andy Shaughnessy is managing editor of *The* PCB Design Magazine. He has been covering PCB design for 15 years. He can be reached by clicking here.

## **BEYOND DESIGN**

# **Controlled Impedance Design**

by Barry Olney

IN-CIRCUIT DESIGN PTY LTD

Controlled impedance—it's all about transmission lines. For perfect transfer of energy, the impedance of the driver must match the transmission line. A good transmission line is one that has constant impedance along the entire length of the line, so that there are no mismatches resulting in reflections. But unfortunately, drivers do not have the exact impedance to match the line (typically 10–35 ohms) so terminations are used to balance the impedance, match the line and minimize reflections.

Reflections occur whenever the impedance of the transmission line changes along its length. This can be caused by unmatched drivers/loads, layer transitions, different dielectric materials, stubs, vias, connectors and IC packages. By understanding the causes of these reflections and eliminating the source of the mismatch, a design can be engineered with reliable performance.

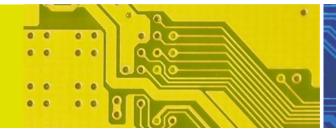

Impedance matching slows down the rise and fall times, reduces the ringing (over/undershoot) of clock drivers and enhances the signal quality of a high-speed design. The ringing is dramatically reduced by adding a series terminator as in Figure 1. From this, we can see that the impedance has to be matched, but to what value?

# MEC FROM UIC

**OPTIMUM TOPOGRAPHY**

**ULTIMATE ADHESION**

**EXCEPTIONAL FLEXIBILITY**

- \* FlatBOND GT Ultimate signal integrity meets ultimate board integrity in this treatment for 25 GHz+ designs. High adhesion with insulation materials; sufficient adhesion for low dielectric resins.

- \* V-Bond 7710 Exceptional inner layer adhesion, substantial cost and maintenance advantages compared with oxide alternatives; flat immersion or spray compatible, broad temperature range.

**EtchBOND CZ-5480** The industry standard bearer for equipment and process flow compatibility; substantially superior to peroxide sulfuric microetchants.

**2030 EtchBOND** The elite adhesion performer provides highest roughness with least material removal.

Uyemura is committed to providing its customers with significant advantages in performance, cost, and maintenance, and to supporting each program with the industry's finest technical support.

For details on MEC products, or to arrange test processing, contact meonta@uyemura.com.

\*Now available for the first time in North America.

UYEMURA USA www.uyemura.com

Figure 1: Unterminated (red) vs. terminated (blue) transmission lines.

For a microstrip transmission line with 3 mil dielectric thickness to ground, a 9 mil trace width is required to match a DDR3 34 ohm driver. Have you ever tried routing matched length DDR3 with 9 mil traces? That ain't gonna work. If the driver's impedance is even lower, say, 22 ohms, then you would need to route 15 mil traces.

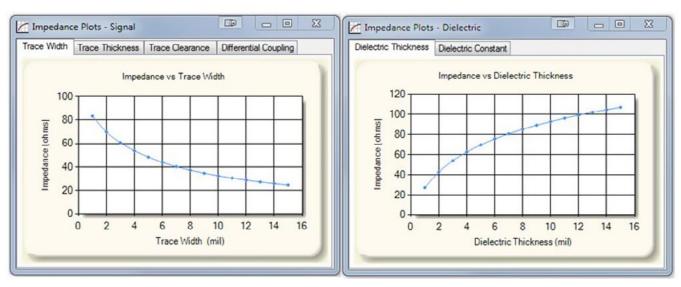

Figure 2 illustrates the plot of impedance vs microstrip trace width (left) and impedance vs dielectric thickness (right). These plots are simulated by multiple passes of the field solver (in the background) to create heads-up graphs of how to adjust the particular variables to achieve the desired impedance. One can see that as the impedance goes down, the trace width increases to a point where it will be unroutable. Also, if we select too low of an impedance, the di/ dt will increase, drawing excessive current from the supply and no doubt creating further power integrity issues.

So, it is a trade-off between trace width, trace (copper) thickness, dielectric thickness

# We deliver Advanced PCB Solutions!

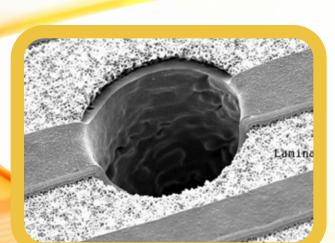

# **Landless Via Technology**

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

**CLICK TO LEARN MORE**

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

# Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

**CLICK TO LEARN MORE**

# **Impedance Tolerance <5%!**

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

**CLICK TO LEARN MORE**

CANDOR INDUSTRIES, INC.

**ADVANCED PCB SOLUTIONS**

Figure 2: The ICD Stackup Planner's impedance plots.

dielectric and constant. Then if you also need to include differential impedance, the trace clearance also comes into play. Plus, one needs to also consider what the preferred fab shop has in stock. So determining the correct variable for your application is not as simple as clicking an impedance "goalseeking" button. But rather, one should weigh up all the pros and cons of changing each variable and make an informed decision. That is exactly what the impedance plots allow you to determine.

Also, as the dielectric constant and loss of all materials varies with frequency, the impedance needs to be simulated at the frequency of the highest bandwidth taking into account the 5<sup>th</sup> harmonic. Traditional, dielectric constant and loss has been

measured at 100MHz but these days a 1GHz (or higher) frequency is more appropriate to be used to determine the impedance.

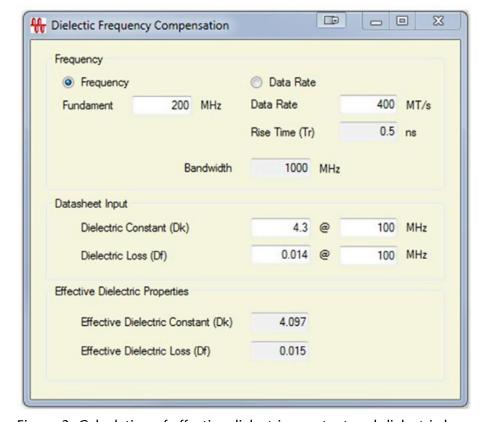

Figure 3: Calculation of effective dielectric constant and dielectric loss.

In Figure 3, a data rate of, say, 400MT/s or a fundamental frequency of 200MHz can be used to determine the maximum bandwidth. From

| 2 Layer     | 4                           | Layer | 6 Lay | ver 8 Layer 1 | 10 Layer 12 Layer     | 14 Layer 16 Layer 18 Lay | er 10L N4000-13 | 1          |                         |                     |                    |                |                   |                                  |                                      |

|-------------|-----------------------------|-------|-------|---------------|-----------------------|--------------------------|-----------------|------------|-------------------------|---------------------|--------------------|----------------|-------------------|----------------------------------|--------------------------------------|

| UNITS       | : m                         | il    |       |               |                       |                          | 4/3/2015        |            |                         |                     |                    |                |                   | Total Board Thic                 | kness: 65.32 mil                     |

|             |                             |       |       |               |                       | Differential Pairs >     | 50/100 Digital  | 40/80 DDR3 | 90 USB                  |                     |                    |                |                   |                                  |                                      |

| ayer<br>No. | Via Span &<br>Hole Diameter |       |       | Description   | escription Layer Name | Material Type            | aterial Type    |            | Dielectric<br>Thickness | Copper<br>Thickness | Trace<br>Clearance | Trace<br>Width | Current<br>(Amps) | Characteristic<br>Impedance (Zo) | Edge Coupled<br>Differential (Zdiff) |

|             |                             |       |       | Soldermask    |                       | Liquid Photoimageable    |                 | 4.0        | 0.5                     |                     |                    |                |                   |                                  |                                      |

| 1           | 8                           | 4     | 8     | Signal        | Top Layer             | Conductive               |                 |            |                         | 1.38                | 10                 | 7              | 0.46              | 41.75                            | 79.92                                |

|             |                             |       |       | Prepreg       |                       | N4000-13; 106; Rc=75%    | (2.5GHz)        | 3.19       | 2.63                    |                     |                    |                |                   |                                  |                                      |

| 2           | ы                           |       |       | Plane         | GND_TOP               | Conductive               |                 |            |                         | 0.71                |                    |                |                   |                                  |                                      |

|             | ы                           |       |       | Core          |                       | N4000-13: 106: Rc=68.3   | % (2.5GHz)      | 3.3        | 2                       |                     |                    |                |                   |                                  |                                      |

| 3           | ы                           |       | 1 1   | Signal        | MidLayer3             | Conductive               |                 |            |                         | 0.71                | 6                  | 4              | 0.19              | 42.97                            | 80.76                                |

|             | ы                           |       |       | Prepreg       |                       | N4203-13EP; 2016; Rc=5   | 4% (2.5GHz)     | 3.60       | 4.67                    |                     |                    |                |                   |                                  |                                      |

| 4           | ы                           |       |       | Signal        | MidLayer4             | Conductive               |                 |            |                         | 0.71                | 8                  | 7              | 0.29              | 41.26                            | 79.79                                |

|             | П                           |       |       | Core          |                       | N4000-13; 1080/106; Ro   | =56.9% (2.5G    | 3.6        | 4                       |                     |                    |                |                   |                                  |                                      |

| 5           | П                           |       |       | Plane         | PWR_TOP               | Conductive               |                 |            |                         | 0.71                |                    |                |                   |                                  |                                      |

Figure 4: Multiple differential pair technologies per substrate.

that, the "effective" dielectric constant and loss can be extrapolated. Unfortunately, most material datasheets specify the dielectric constant (Dk) and dielectric loss (Df) at 100MHz. This is the traditional test parameter, however, that is now changing with the next generation of highspeed, low-loss laminates that are specified up to 10GHz or more. Some low loss microwave materials are measured at 100GHz.

Typically for a digital design, a characteristic impedance of 50-60 ohms is used. But, this becomes more important as the edge rates become faster and different technologies have their specific requirements. For example: Ethernet is 100 ohm and USB 90 ohms differential, DDR2 is 50/100 and DDR3/4 is 40/80 single-ended/differential impedance. So controlling impedance with a number of different technologies can become a challenge. Also, as operating voltages are reduced, the associated noise margins are also reduced, making it even more important to match the impedance.

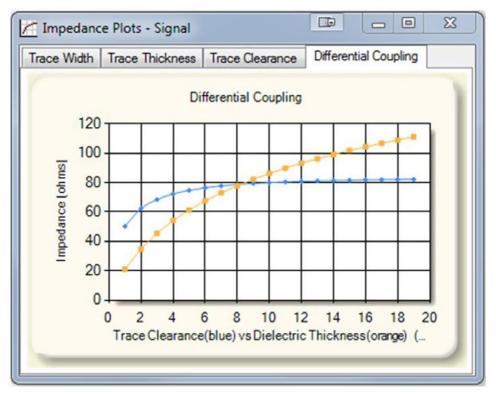

Figure 4 illustrates the ICD Stackup Planner's unique differential pair calculation. In this case, digital, DDR3 and USB technologies are all accommodated on Nelco N4000-13, 2.5GHz material.

With differential impedance, there comes a (coupling) point whereby increasing the trace separation or the dielectric thickness has little or no further effect on impedance. At this point, the impedance rolls off and the traces become uncoupled. This is also the point where crosstalk of unrelated signals begins to occur.

For the microstrip stackup of Figure 4, Figure 5 shows this differential coupling point at 8 mils. So, where I have a 10 mil trace clearance for the 79.92 ohms differential impedance, I should have backed this off to just 8 mil trace clearance in order to maintain sufficient coupling otherwise the two traces begin to act as individual single ended signals of 41.75 ohms.

For crosstalk, 8 mils (in this case) is also the minimum separation before coupling occurs. This gives you a defined clearance rule to constrain routing, in order to avoid edge coupled crosstalk of long parallel trace segments.

In conclusion, controlled impedance design is not just a matter of pushing a button to get the right trace width for the desired impedance. It is an interactive process of manipulating five variables in combination with the material your preferred fab shop stocks to achieve an educated result. Your product will not only be manufacturable, but also exhibit improved signal quality, reduced crosstalk and electromagnetic radiation and also perform reliably over many years.

# **Points to Remember**

- A good transmission line is one that has constant impedance along the entire length of the line.

- The impedance of the driver must match the transmission line to avoid reflections.

- Drivers do not have the exact impedance to match the line (typically 10–35 ohms).

- Impedance matching slows down the rise and fall times, reduces the ringing (over/under-

Figure 5: Multiple field solver passes produce differential coupling plot.

shoot) of clock drivers and enhances the signal quality of a high-speed design.

- Impedance plots are simulated by multiple passes of the field solver to create heads-up plots of how to adjust the particular variables to get the desired impedance.

- If you select too low of an impedance, the di/dt will increase, drawing excessive current form the supply and no doubt, creating further power integrity issues.

- Controlling impedance is a trade-off between trace width, trace (copper) thickness, dielectric thickness, dielectric constant and trace clearance.

- The dielectric constant and loss of all materials varies with frequency.

- Multiple differential pair technologies should be accommadated on the same substrate.

- The coupling point is where increasing the trace separation or the dielectric thickness has little or no further effect on differential impedance. At this point, the impedance rolls off and the traces become uncoupled. This is also the

point where crosstalk of unrelated signals begins to occur. PCBDESIGN

### References

- 1. Barry Olney Beyond Design columns: Embedded Signal Routing, Impedance Matching.

- 3. Eric Bogatin, Signal and Power integrity Simplified.

- 4. Lee W. Ritchey, How and why of obtaining accurate impedance calculations.

- 5. The ICD Stackup and PDN Planner is available at: www.icd.com.au.

Barry Olney is managing director of In-Circuit Design Pty Ltd (ICD), Australia. The company developed the ICD Stackup Planner and ICD PDN Planner software, is a PCB Design

Service Bureau and specializes in board level simulation. To read past columns, or to contact Olney, click here.

# Ventec at your fingertips.

Direct access to all the news and technical updates from Ventec is now at your fingertips thanks to the user-friendly new Ventec app, which gives up-to-the-minute information on all developments, ongoing projects, appointments and technical data updates from Ventec International Group.

With this free app, you can:

- Get the latest news from all of Ventec's operations worldwide

- Access the latest datasheets and process guidelines

- Be notified when new datasheets are available for download

# Download yours today!

Wherever technology takes you, we deliver.

# ventec

# THE BARE (BOARD) TRUTH

# The Do's and Don'ts of Signal Routing for Controlled Impedance

by Mark Thompson, C.I.D.

PROTOTRON CIRCUITS

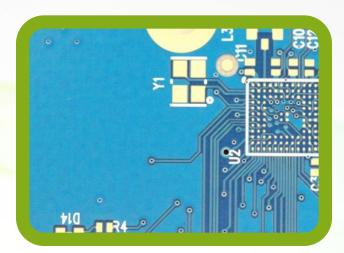

In this column, we will once again be focusing on controlled impedance structures, both from the layout side and the simulation side. I will break them down into the sub-categories of the models they represent and the important points to remember when using the various models. I will also be asking questions such as, "Why would a fabricator ask for a larger impedance tolerance?" and "Where does the fabricator draw the line for controlling various structures?"

Later, I will break down my Top 10 do's and don'ts of signal routing.

# A Few Rules of Thumb

Let's start with single-ended structures, both co-planar and those in "free space," i.e., not coupled to any adjacent copper pour.

For external single-ended structures starting with quarter or half-ounce copper, the trace width is typically about twice the dielectric needed between the impedance signal and its reference plane.

Example: A 4.25 mil trace needs about a .0026"–.0028" dielectric to be a reference plane for 50 ohms on half-ounce starting copper (1.5 ounces after plating).

# Pulsonix **Advanced Schematic** Capture and PCB Design Software

# A refreshing approach to simplifying Schematic Capture and PCB Design

- Import filters for all major tools (designs and libraries)

- Very easy to learn and use

- 5-Star Service and Support

**Download a Free Trial**

info@pulsonix.com www.pulsonix.com

### THE DO'S AND DON'TS OF SIGNAL ROUTING FOR CONTROLLED IMPEDANCE continues

Keep the copper pour that resides on the impedance layer a minimum of 3x the chosen trace width for impedance; this ensures no unwanted co-planar coupling occurs. At larger trace widths upwards of .012" this distance can be as little as 2x the trace width.

## **Differential Pairs**

Be sure you match the lengths of each half of the differential pair. Make sure the same space is maintained throughout the run, with the exception of neck-down areas at the terminations.

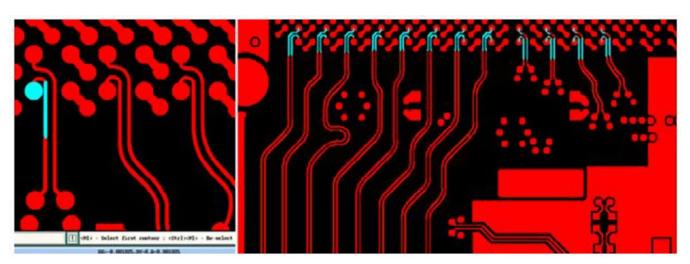

Be careful when terminating differential pairs that you do not create same net space violations where smaller traces (neck-downs) terminate. See Figure 1.

# Q: Why is this a problem?

A: If the same net space violation is LESS than the fabricator's specified minimum space value and the fabricator is not aware these neckdown areas are part of larger/longer differential pairs, they may "fill" the space violation.

# Q. And why, exactly, is that a problem?

A. If a fabricator "fills" in the same net space violation, we have just changed the LENGTH of the differential pair!

Having said that, a fabricator will not solve for these small neck-down sections, only the larger, longer run of the same diff pair. This is true of SE structures as well. Really, anything less than about .3mm in length cannot be controlled to any great degree.

The same is true for surface single-ended or differential pairs that have the vast majority of the run on one layer and only pick up the diff pair on the opposing side in very short lengths.

What are some reasons a fabricator may ask for a wider impedance tolerance?

- For lines less than .1 mm: Here, many times a fabricator asks for +/-15%, but not because they think they are not going to hit the number. Remember that 10% of a .1 mm trace is 4/10 of a mil, less than half a mil! Hence many shops ask for 15% for traces .004" and below.

- Additionally, the fabricator may ask for 15% due to less-than-predictable surface finishes. Let's say the part has either epoxy-filled or silver-epoxy-filled vias and the fabricator is outsourcing. The epoxy or silver-fill process itself requires that the material be pushed into the holes under pressure. After curing, they typically "planarize," basically grinding down the surface so it is flat, and herein lies the rub. If the planarization process is not perfect, there can be quarter to half a mil difference end-to-end on the surface topography, making it more difficult to properly predict impedances.

# The 10 Do's and Don'ts

1. **Do** consult with your fabricator regarding any controlled impedances at your earliest pos-

Figure 1: Differential pairs create same net spacing violation at termination points.

# INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

# Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

> **CONTACT YOUR SUPPORT TEAM TODAY**

www.rogerscorp.com

# MEET YOUR COOLSPAN® **TECA FILM SUPPORT TEAM**

Leading the way in...

• Support • Service • Knowledge • Reputation

# SCAN THE CODE TO GET OUR CONTACT INFO.

Dale Doyle Western Territory

John Dobrick

Scott Kennedy

John Hendricks

**Kent Yeung** Regional

Sales Director

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

## THE DO'S AND DON'TS OF SIGNAL ROUTING FOR CONTROLLED IMPEDANCE continues

sible convenience. Don't assume that specifying "dielectric only" will meet your impedance requirements.

- 2. **Do** make sure your diff pairs have the same space throughout the run and are of matched length. **Don't** assume the odd-mode impedance is half the differential pair value.

- 3. **Do** keep copper 3x the trace width away from the impedance trace if no co-planar coupling is wanted. **Don't** vary the ground separation distance on the same layer. Keep all the ground separation distances the same on a given layer for all co-planar impedances.

- 4. **Do** ensure that all structures have a proper reference plane. **Don't** place differential pairs over large splits on a plane layer.

- 5. **Do** remember Dk decreases as frequency increases. **Don't** assume that all shops know this.

- 6. **Do** stick to calling out the desired material by its 4101/ number. **Don't** assume all materials are the same.

- 7. **Do** add any bumps in differential pairs, in an effort to match lengths, somewhere away from the terminations. **Don't** wrap around a termi-

nation point, creating same net spacing violations.

- 8. **Do** terminate traces in the center of the pad. **Don't** terminate traces at the edge of the pad or device.

- 9. **Do** consult your fabricator for minimum routing gaps for the desired copper weight. **Don't** rely on data sheets alone for proper Dk and Df info at a specific speed.

- 10. **Do** make sure that what you have specified on the drawing for impedance trace widths actually exists. **Don't** call out impedances solely by their net names.

Please feel free to contact me with any questions or comments. PCBDESIGN

Mark Thompson is in engineering support at Prototron Circuits. His column, The Bare (Board) Truth, appears bimonthly in The PCB Design Magazine. To read past columns, or to

contact Thompson, <u>click here</u>, or phone 425-823-7000, ext. 239.

# **New Stream for Topological Quantum Computer Research**

Heterointerfaces composed of dissimilar materials have been applied to transistors and LEDs. In particular, the best-quality electron sys-

tem is formed in gallium arsenide heterostructures, where a unique quantum phase was found at low temperature about 30 years ago. This quantum phase is expected to be applied for a new type of topological quantum computer which possesses dramatically improved

Researchers at the Quantum Phase Electronics Center/Department of Applied Physics, the Graduate School of Engineering at the University of Tokyo, headed by Professor Masashi Kawasaki, in collaboration with a group headed by Dr. lurgen Smet at the Max Planck Institute, have

> fabricated ZnO heterostructures of unprecedented high quality, and observed the quantum phase in a material other than a GaAs heterostructure for the first time.

> This research has been published in the online edition of Nature Physics.

# Solutions to Ensure PCB Manufacturing Success!

# **CAM350**

Verify and Optimize PCB Designs for Successful Manufacturing.

# BluePrint-PCB

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB post processing needs.

For more information please visit downstreamtech.com or call 800-535-3226.

# THE PULSE

# Impedance Control, Revisited

# by Martyn Gaudion

**POLAR INSTRUMENTS**

Surprising me on a regular basis is the way that demand for impedance control continues to extend into a broader range of product. After some 20 years of involvement in this field, I would have expected that everyone who needed to consider impedance control would have the capability nailed. Fortunately, that's not the case, and a steady stream of "how to" questions keep coming my way.

The positives for new fabricators and designers lie in the fact that, even though impedance control may be new to them, there is a wealth of information available. Some of this information is common sense and some is a little counterintuitive. So, this month I'd like to go back to the fundamentals, and even if you are an experienced hand at the subject, it can be worth revisiting the basics from time to time.

# **Standards**

It's worth remembering that traceable reference impedance standards are available and all impedance measurement systems should be able to be compared to a traceable standard. The reference air line is the de facto standard for impedance—a precision manufactured coaxial standard "air" referring to the fact that air is employed as the dielectric in this type of precision reference line.

Because a closed-form equation exists for the impedance of a coaxial structure, air lines may be calibrated by national standards bodies who can strip down the line and make precise measurements of the internal diameter of the outer body and the external diameter of the inner conductor. The bore measurement is usually made with a technique called air gauging,

# YOUR DESIGN ISN'T COMPLETE UNTIL THE BOARD IS IN YOUR HAND.

Because customer service is our number one priority, we provide engineering support to all of our customers to ensure your design is always correct.

Complete PCB engineering support, just another reason we are

**America's Board Shop**

WHAT OUR CUSTOMERS SAY

# Prototron Circuits

Selling time since 1987

prototron.com | sales@prototron.com

# **IMPEDANCE CONTROL, REVISITED** continues

Figure 1: Traceable 50 ohm air line standard with SMA adaptor.

which involves inserting a precision piston into the bore and measuring the resistance to air passing through the piston into the bore. It's a science in its own right and an interesting subject if you happen to be into mechanical metrology.

Now, back on track with impedance. The availability of air line standards allows measurement systems manufacturers to prove accuracy traced back to a national standard. Air lines are commonly available in impedances of 50, 75, and 100 ohms, and, more rarely, 28 ohm air lines.

Why 28 ohms? Well, this was the impedance of Rambus RAM data lines, and back in the day when that technology was introduced the impedance requirements were demanding and led to 28 ohm air lines being developed as a standard for that application. A side benefit of the availability of 28 ohm lines is the ability to traceably calibrate a TDR over a very broad range of commonly used impedances. At a lower cost, but also providing an economic alternative to air lines, semi-rigid precision coax can be used as a transfer standard and has the benefit of robustness if used in a production environment.

# **Expectations**

Newcomers to impedance control are sometimes tempted to tie down specifications more tightly than is practical. Perhaps this arises because the units of lossless impedance are ohms, and it is customary to expect that something specified in ohms (resistance) can be specified very tightly indeed. However, you have to remember that impedance is in fact a high-frequency characteristic of a transmission line, and in general the higher the frequency gets the less realistic it is to think you can specify down to fractions of an ohm or less. In fact, the traceable

air line standards mentioned earlier in this article may have an uncertainty of 0.2-0.5 ohms, and that's for a reference line possibly costing many hundreds of dollars. So you would not expect a line based on the finest geometry possible on an FR-4 board to come even close to those levels. Often impedance is ±10%; tighter specs may demand ±5% and some critical applications may be more tolerant of higher or lower impedances—so you may encounter specs of say 50 ohms +7 ohms – 4 ohms, for example.

# **Test coupons**

As frequency increases the test coupon (sometimes called the test vehicle) becomes an increasingly important part of the measurement system as, coincidentally, do the probes and the interconnect cables to the measurement system. Careful design of the coupon ensures that artefacts which could spoil the measurement quality are minimised.

Launch pad diameter is a compromise between ease of probing and launch aberrations; having a coupon that is long enough (IPC still specifies 6"/150 mm) gives an adequate sample of the trace to measure over a reasonable length of PCB; after all, the impedance test is meant to measure the consistency as well as the absolute value of the fabricated impedance. Also, coupons should be designed to ensure that any nomenclature in the copper is well away from the trace under test and that the transmission lines are back away from the coupon edges to avoid any effects on impedance from the proximity of the edge of the ground plane. Likewise, on the coupon power and ground planes should be interconnected—but not on the PCB itself!

# **Modelling**

Coaxial standards can be calculated with precise closed loop equations. However, PCB transmission lines are far from uniform cylindrical coaxial structures. At their simplest they could be regarded as rectangular traces over infinite planes, and whilst approximations do exist for calculating the basic variations of such structures, they are limited when pushed to modern trace geometries, which leaves you requiring a field solver if you wish to make ac-

# DYMAX CONFORMAL COATINGS. BETTER PROTECTION AND HIGHER THROUGHPUT. BEYOND A SHADOW OF A DOUBT.

# LIGHT-CURE CONFORMAL COATINGS

Dymax Conformal Coatings cure in seconds with UV light – and with ambient moisture curing available for shadowed areas, you can be confident you're getting maximum protection – even underneath components. Add vivid blue fluorescing for easy inspection of coating coverage, and you'll see more throughput, in less time, using less floor space. All with unsurpassed protection against moisture, dust, chemicals, and temperature cycling. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. Visit **dymax.com/pcbcoating** to download the new *Guide to Light-Cure Conformal Coatings*.

# **IMPEDANCE CONTROL, REVISITED** continues

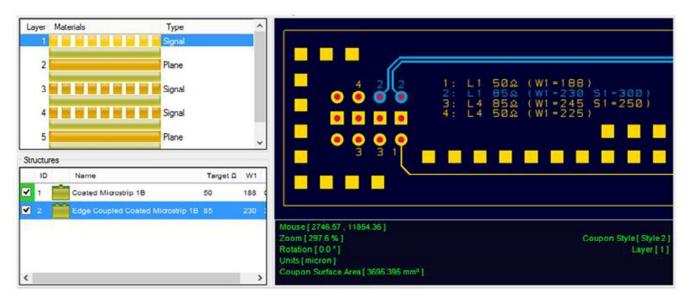

Figure 2: Impedance coupon generation software.

curate calculations. All solvers obey the laws of physics and for the same data in should give the same impedance out. When choosing a solver you should look for one that permits you to model the layered substructure of the PCB, take into account the trapezoidal nature of the traces and where possible account for resin rich layers or areas of resin richness between differential pairs. The ability to run sensitivity analysis is a useful enhancement too.

## Modelled vs. Measured

The aim of modelling is to get you as close to the desired result in the shortest number of iterations, ideally, right first time; it is worth keeping an open mind when looking at correlation of measured vs modelled impedance. Modelling predicts the uniform impedance of a uniform trace in a homogenous medium. It's good to ask yourself a few questions when faced with less correlation than you expect. First, never assume anything. Look at both the measured and modelled and see if there are areas which need attention; often, a 5 or 10 ohm mismatch between modelled and measured can be comprised of an ohm here an and ohm there. And you can suddenly find 5 or 6 ohms hiding from your initial assumptions.

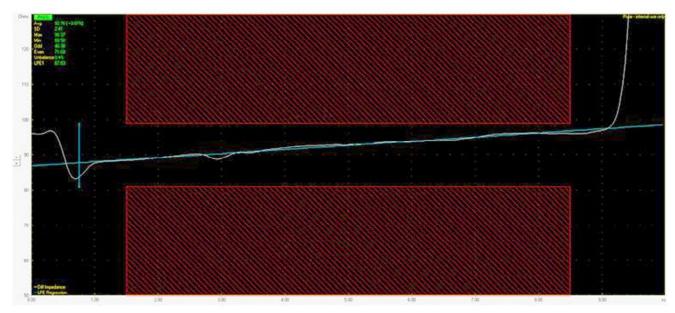

First, did you assume you made what you think you made? A microsection is a wise step

to confirm actual geometries. Second, look at the impedance trace—does it slope? This could be from trace taper or, on thin traces, trace resistance. Or does it dip at the start or the end, implying that the coupon design or the setting of test limits is not optimised? On the modelling side, has the trapezoidal shape of the trace been considered? Have you run sensitivity analysis to see which trace parameter has the largest contribution to any error? Attention to the above makes you better prepared to optimise correlation on the next spin. I mentioned sloping traces: if not down to taper, this could be because you are using sub 75 micron lines on thin copper—and here you would need to consider measuring instantaneous impedance using a technique such as launch point extrapolation.

# **Occasionally Expect the Unexpected**

From time to time you might experience results that seem too consistent. This was the experience of one of our fabricator customers who accidentally set a TDR to measure the end of the cable and not the coupon. Unsurprisingly, the TDR reported very repeatable results all within a fraction of 50 ohms. If your measurements are too consistent, you might be measuring the wrong thing; for example, another fabricator customer etched the PCB part number in the ground plane

# **IMPEDANCE CONTROL, REVISITED** continues

Figure 3: Incident impedance measurement by LPE method. (For more detail, see my February 2015 column, 13: Incident, Instantaneous, Impedance).

over a stripline structure, causing the impedance to increase because of the lack of copper in the return path. As with any measurement system, awareness of what to expect and what not to expect and having the tools to predict what ought to be happening are essential to providing reliable and consistent results. **PCBDESIGN**

Core Gate

Martyn Gaudion is CEO of Polar Instruments. To contact him, click here.

# **Novel Nanotube Tunnel FET Architecture**

Classical semiconductor physics suggests that a single charge transport CMOS (complementary metal-oxide-semiconductor) device cannot achieve ultrahigh-performance and ultra-low-standby-power at the same time. Nanoelectronics researchers are trying to design devices that hit the 'sweet spot', i.e. where a charge transport device can provide its highest performance at its lowest power consumption, especially in its 'off' state.

Now, researchers from the Integrated Nanotechnology Lab at King Abdullah University of Science and Technology (KAUST) show a unique device concept which combines the advantages of a tunnel field-effect transistor (TFET) for ultralow OFF (leakage) current and ultra-steep sub-threshold slope for sharper and faster ON and OFF switching due to the FET's nanotube architecture.

In addition, this nanotube device, which is built on heterogeneous material systems, shows scalability and area efficiency in an unprecedented way. According to the scientists, this is the highest comprehensive functionality achieved ever in single device.

"We capitalized on an innovative design of nanotube architecture with a core (inner) gate and a shell (outer) gate," Muhammad Mustafa Hussain, an Associate Professor of Electrical Engineering at KAUST, tells

> Nanowerk. "This way we were able to achieve utmost electrostatic control for ultra-low-standby-power operation."

> The team reports their findings in the April 29, 2015 online edition of Scientific Reports ("InAs/Si Hetero-Junction Nanotube Tunnel Transistors").

# **PCB007** Highlights

# **Multek CTO Excited about the Challenges** of Fast-Moving Wearables Market

I-Connect007 Publisher Barry Matties and recentlyappointed Multek CTO Dr. Joan Vrtis sat down at IPC APEX EXPO to discuss the rapidly evolving wearables market, especially for medical, and the myriad questions that must be addressed. Other topics include Multek's contribution to the wearables industry and what it sees as the main challenges to putting their circuits into various applications.

# Raising a Unified Voice for an Advanced **Manufacturing Economy**

The electronics manufacturing industry is an important sector in the global economy, and John Hasselmann, VP of Government Relations at IPC, is an advocate for policies that will help our industry as well as the prosperity and welfare of billions of people.

# **Reliability and Harmonization of Global** Standards at Forefront of EIPC Efforts

At IPC APEX EXPO 2015, I-Connect007 Technical Editor Pete Starkey caught up with EIPC's Michael Weinhold and Alun Morgan, who were happy to discuss both recent and ongoing focuses for EIPC. Also touched on was the importance of the alignment of global standardization processes, especially for Asia.

# **Are There Advantages to Changing Your Registration System?**

I-Connect007 Publisher Barry Matties recently had a conversation with DIS's Tony Faraci at IPC APEX EXPO 2015, to learn more about their pinless registration system. What was most interesting to Matties was the potential advantages a pinless system offers and why the process has not been widely adopted.

# Schmoll Keeping an Eye on the Future and on LDI

In this interview, Thomas Kunz, who has been at the helm of Schmoll Maschinen as president since 1993, discusses the company's lengthy history in mechanical engineering (more than 70 years), current global scope, and what he sees as a steady progression in directions that make the most sense to customers, which includes laser direct imaging.

# **Bernie Kessler: Pioneering Spirit Then and Now**

I-Connect007's Patty Goldman sat down with long time friend and IPC Hall of Famer Bernie Kessler at IPC APEX EXPO 2015 in San Diego. Among other things, the two discussed the early days of IPC and the origins of APEX EXPO.

# **Manz: A Total Process Solution**

At the recent CPCA Show in China, I-Connect007 Publisher Barry Matties had a chance to speak with Alex Liu, the deputy general manager of the PCB business unit for Manz. Manz has focused on creating a process from direct imaging to wet processing. With more entrants into the direct imaging arena, Liu feels that this approach gives Manz and their customers an advantage.

# **ESI's New Gemstone Changing the Rules for Laser**

I-Connect007 Publisher Barry Matties sat down at CPCA 2015 with ESI's Mike Jennings, who explained the company's newest addition: Gemstone, an ESI-designed and manufactured laser system with 10,000 guaranteed hours, which is poised to change the rules in flex and other printed circuit processing.

# **Key PCB Makers Strategize to Meet Industry Demands**

The computer/peripheral application is expected to witness the highest growth followed by the communication applications. Nippon Mektron, Zhen Ding Technology Holding Limited, Young Poong Electronics Co. Ltd., Unimicron Technology Corp., and Samsung Electro-Mechanics are among the major suppliers of PCBs.

# N.A. PCB Book-to-Bill Ratio Strengthens

"Although North American PCB sales continued slightly below last year's levels in February, bookings strengthened," said Sharon Starr, IPC's director of market research. "This increased the bookto-bill ratio...it has been in positive territory for the past five months, which is a positive indicator for sales growth in the first half of 2015."

# How can you find the best PCB Partner? We can tell you. We wrote the book on it.

Choosing a PCB partner isn't hard—if you know what to look for. We've broken it down into "The 5 Commandments" and you can download it for free.

We are proud to be the Circuit Board Manufacturer of more than 400 growing companies, and even prouder to be a good partner for all our customers!

Click to Download

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

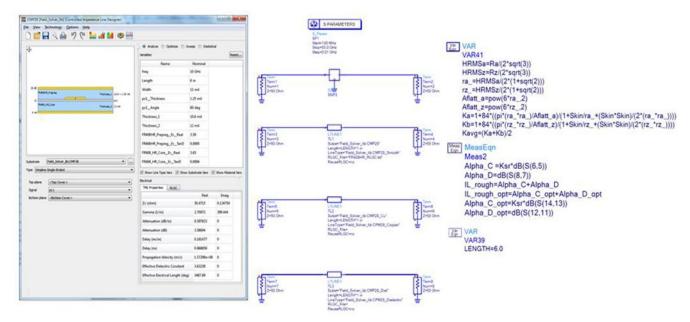

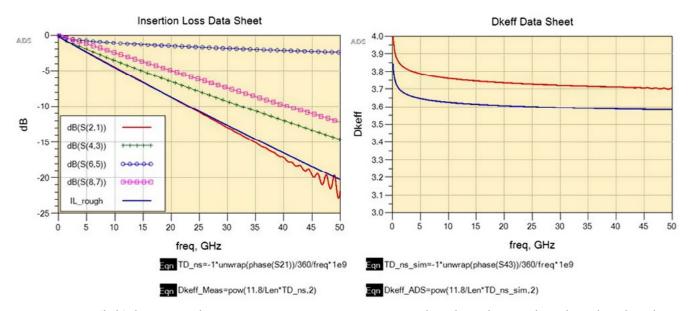

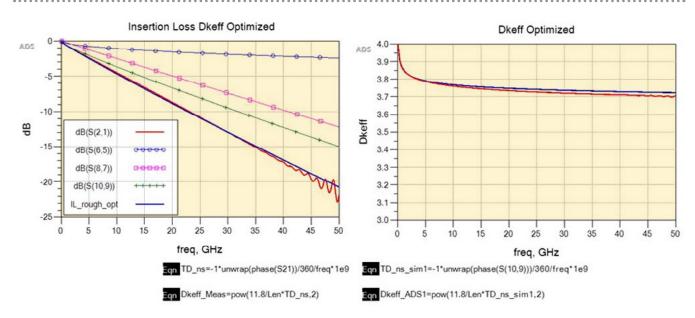

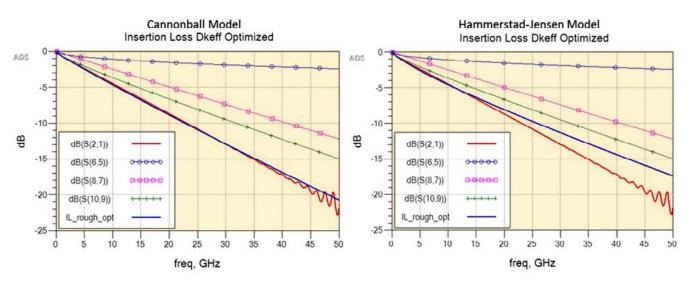

# by Bert Simonovich

LAMSIM ENTERPRISES

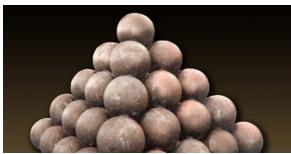

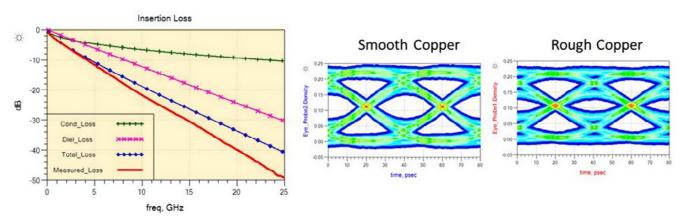

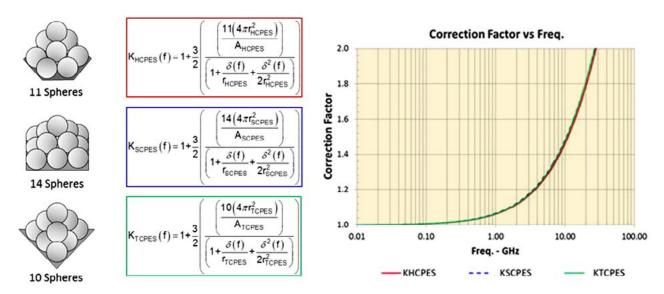

In the GB/s regime, accurate modeling of conductor losses is a precursor to successful high-speed serial link designs. Failure to model roughness effects can ruin you day. For example, Figure 1 shows the simulated total loss of a 40-inch PCB trace without roughness compared to measured data. Total loss is the sum of dielectric and conductor losses. As can be seen, with just -3dB delta in insertion loss between simulated and measured data at 12.5 GHz, there is half the eye height opening with rough copper at 25GB/s.

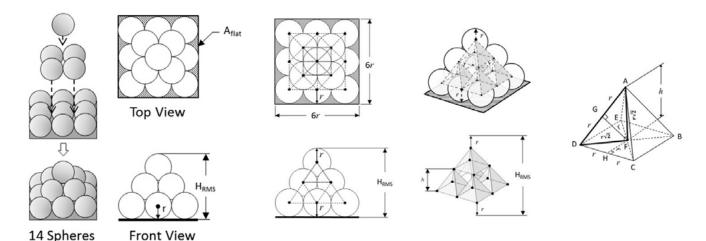

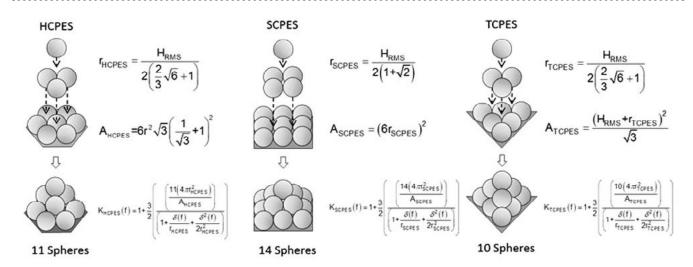

According to Wikipedia, close-packing of equal spheres is defined as "a dense arrangement of congruent spheres in an infinite, regular arrangement (or lattice)" [8]. The cubic closepacked and hexagonal close-packed are examples of two regular lattices. The cannonball

stack is an example of a cubic close-packing of equal spheres, and is the basis of modeling the surface roughness of a conductor in this article.

So what do cannonballs have to do with modeling copper roughness anyway? Well, other than sharing the principle of close packing of equal spheres, and having a cool name, not very much.

# **Background**

In PCB construction, there is no such thing as a perfectly smooth conductor surface. There is always some degree of roughness that promotes adhesion to the dielectric material. Unfortunately this roughness also contributes to additional conductor loss.

Electro-deposited (ED) copper is widely used in the PCB industry. The manufacturing process sees a large rotating drum, made of polished stainless steel or titanium, which is partially submerged in a bath of copper sulfate solution. The cathode terminal is attached to the drum.

# IT'S FULLY CAPABLE **AFFORDABLY PRICED TOTALLY SCALABLE** AND TRUTH BE TOLD THERE'S NOTHING STANDARD ABOUT IT

# OrCAD PCB Designer Standard

When your standards are incredibly high, even your standard software is exceptional. OrCAD® PCB Designer Standard combines cutting edge capabilities with tremendous user value making it an intelligent choice for startups and entreprenuers. Industry standard schematic capture, PCB editing, and mechanical collaboration all come standard for as little as \$1300. OrCAD PCB Designer Standard gets your project started on a solid foundation with the scalable design tools that can grow with your business.

See how affordable OrCAD can be: Learn More >

## CANNONBALL STACK FOR CONDUCTOR ROUGHNESS MODELING continues

Figure 1: Comparisons of measured insertion loss of a 40-inch trace vs simulation. Eye diagrams show that with -3dB delta in insertion loss at 12.5 GHz there is half the eye opening at 25GB/s. Modeled and simulated with Keysight EEsof EDA ADS software.

while the anode terminal is submerged in the solution. A DC voltage supplies the anode and cathode with the correct polarity.

As the drum slowly rotates, copper is deposited onto it. A finished sheet of ED copper foil has two sides. The matte side faces the copper sulfate bath, while the drum side faces the rotating drum. Consequently, the drum side is always smoother than the matte side.

The matte side is usually attached to the prepreg sheets, prior to final pressing and curing, to form the core laminate. Prepreg is the term commonly used for a weave of glass fiber yarns pre-impregnated with resin which is only partially cured. To enhance adhesion, the matte side has additional treatment applied to roughen the surface. For high frequency boards, sometimes the drum side of the foil is laminated to the core. In this case it is referred to as reversed treated (RT) foil. Even after treatment, it is still smoother than standard treated foils.

Various foil manufacturers offer ED copper foils with varying degrees of roughness. Each supplier tends to market their product with their own brand name. Presently, there seems to be three distinct classes of copper foil:

- Standard

- Very-low profile (VLP)

- Ultra-low profile (ULP) or profile free (PF)

Some other common names referring to ULP class are HVLP or eVLP.

In lieu of scanning electron microscopy (SEM) analysis, profilometers are often used to quantify the roughness tooth profile of electrodeposited copper. Tooth profiles are typically reported in terms of 10-point mean roughness (R<sub>z</sub>) for both sides, but sometimes the drum side reports average roughness (R<sub>2</sub>) in manufacturers' data sheets. Some manufacturers also report RMS roughness ( $R_a$ ).

# **Modeling Roughness**

Several modeling methods were developed over the years to determine a roughness correction factor (K<sub>sr</sub>). When multiplicatively applied to the smooth conductor attenuation  $(\alpha_{\text{smooth}})$ , the attenuation due to roughness  $(\alpha_{rough})$  can be determined by:

$$\alpha_{rough} = K_{SR} \alpha_{smooth}$$

Equation 1

The most popular method, for years, has been the Hammerstad and Jensen (H&J) model, based on work done in 1949 by S. P. Morgan. The H&J model assumes a triangular corrugated surface, representing the tooth structure of rough copper. It was thought that when the skin depth is small, compared to the tooth height, current begins to flow along the corrugated surface; thereby increasing its loss due to the longer path length. However, the theory breaks down from a physics perspective because there is no evidence of additional time delay

## CANNONBALL STACK FOR CONDUCTOR ROUGHNESS MODELING continues

(TD), compared to the fixed spatial length of the trace.

The H&J roughness correction factor  $(K_{HJ})$ , at a particular frequency, is solely based on a mathematical fit to S. P. Morgan's power loss data and is determined by [2]:

$$K_{HJ} = 1 + \frac{2}{\pi} \arctan\left(1.4\left(\frac{\Delta}{\delta}\right)^2\right)$$

Equation 2

Where:

$K_{HJ}$  = H&J roughness correction factor;  $\Delta$  = RMS tooth height in meters;

$\delta$  = skin depth in meters.

Alternating current (AC) causes conductor loss to increase in proportion to the square root of frequency. This is due to the redistribution of current towards the outer edges caused by skineffect. The resulting skin-depth ( $\delta$ ) is the effective thickness where the current flows around the perimeter and is a function of frequency.

Skin-depth at a particular frequency is determined by:

$$\delta = \sqrt{\frac{1}{\pi f \mu_0 \sigma}}$$

Equation 3

Where:

$\delta$  = skin-depth in meters;

f = sine-wave frequency in Hz;

$\mu_0$ = permeability of free space =1.256E-6 Wb/A-m;

$\sigma$  = conductivity in S/m. For annealed copper  $\sigma = 5.80E7$  S/m.

The model has correlated well for microstrip geometries up to about 15 GHz, for surface roughness of less than 2 RMS. However, it proved less accurate for frequencies above about 5 GHz for very rough copper [3].

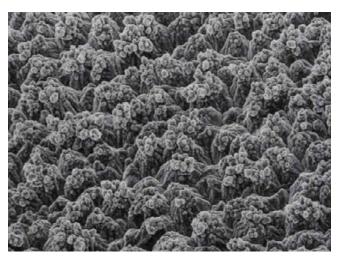

In recent years, the Huray model [4] has gained popularity due to the continually increasing data rate's need for better modeling accuracy. It takes a real-world physics approach to explain losses due to surface roughness. The model is based on a non-uniform distribution of spherical shapes resembling snowballs and stacked together forming a pyramidal geom-

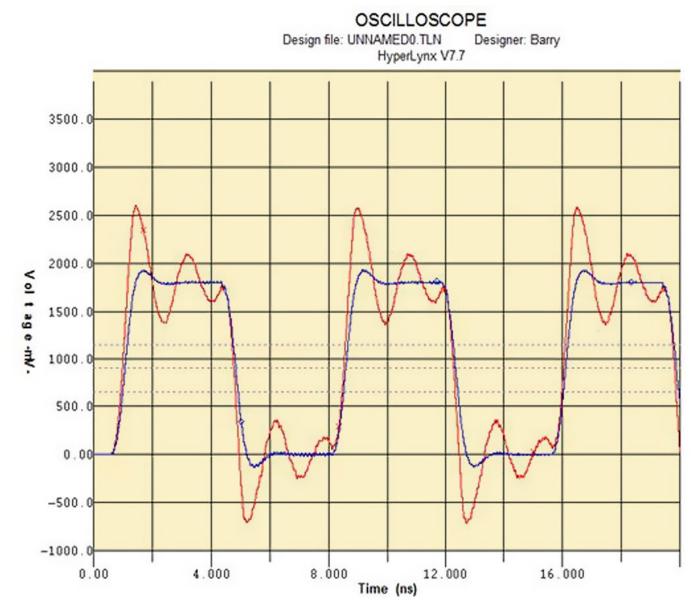

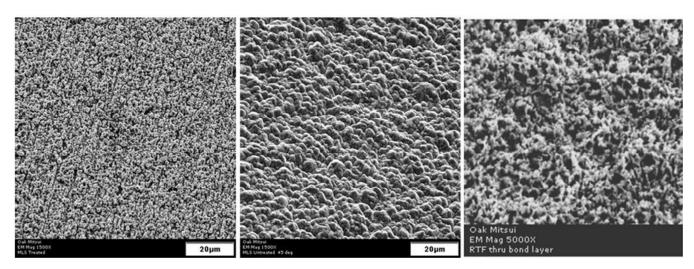

Figure 2: SEM photograph of electrodeposited copper nodules on a matte surface resembling snowballs on top of heat treated base foil. Photo credit Oak-Mitsui.

etry, as shown by the SEM photo in Figure 2.

By applying electromagnetic wave analysis, the superposition of the sphere losses can be used to calculate the total loss of the structure. Since the losses are proportional to the surface area of the roughness profile, an accurate estimation of a roughness correction factor (K<sub>SRH</sub>) can be analytically solved by [1]:

$$K_{SRH}(f) = \frac{A_{matte}}{A_{flat}} + \frac{3}{2} \sum_{i=1}^{j} \frac{\left(\frac{N_{i} \times 4\pi a_{i}^{2}}{A_{flat}}\right)}{\left(1 + \frac{\delta(f)}{a_{i}} + \frac{\delta^{2}(f)}{2a_{i}^{2}}\right)}$$

**Equation 4**

Where:

$K_{SRH}$  (f) = roughness correction factor, as a function of frequency, due to surface roughness based on the Huray model;

$\frac{A_{matte}}{A_{matte}}$  = relative area of the matte base compared  $A_{flat}$ to a flat surface;

$a_i$  = radius of the copper sphere (snowball) of the i<sup>th</sup> size, in meters;

$\frac{N_i}{A_{flat}}$  = number of copper spheres of the i<sup>th</sup> size per unit flat area in sq. meters;

$\delta$  (f) = skin-depth, as a function of frequency, in meters.

### CANNONBALL STACK FOR CONDUCTOR ROUGHNESS MODELING continues

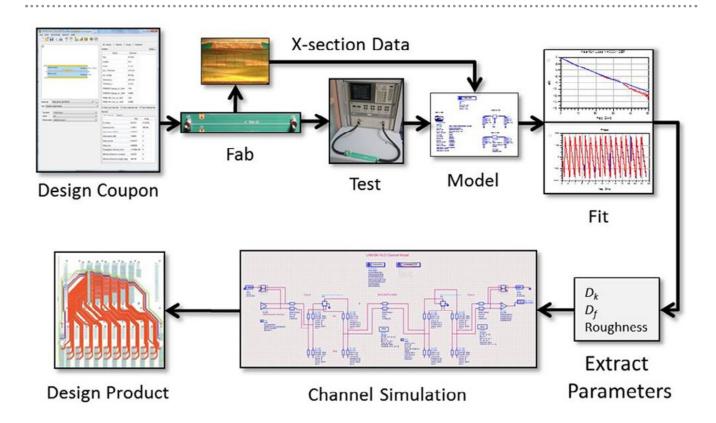

The design feedback method [7], as illustrated in Figure 3, is another practical way to model conductor roughness and extract material properties. The idea here is to design and fabricate a test coupon using the dielectric material and copper foil roughness you plan on using in the final design. After measuring and cross-sectioning a sample, you would bring this data into a circuit simulator, and then fit the simulation to match insertion loss and phase. You would then use the extracted parameters in your real design simulation and finally designing the actual product.

Although this method is quite practical and accurate, obtaining good measured data requires considerable effort. First a high level of expertise is required to design the test coupon. Next expensive test equipment and skill is required in the measurement and de-embedding of the fixture. Finally, considerable expertise and know-how is needed to tune the right parameters such that the final model fits both insertion loss and phase. All this adds up to increased time and dollars, and is beyond the scope and resources of many companies.

### **Cannonball Model**

This leads us to the Cannonball model. Using the concept of cubic close-packing of equal spheres, the radius of the spheres (ai) and tile area (A<sub>flat</sub>) parameters for the Huray model can now be determined solely by the roughness parameters published in manufacturers' data sheets.

This model is a follow-up research to my recent DesignCon2015 paper titled Practical Method for Modeling Conductor Surface Roughness Using Close Packing of Equal Spheres [1]. In that paper I presented a similar model using hexagonal close-packing of equal spheres.

Since losses are proportional to the surface area of the roughness profile, the Cannonball model can be used to optimally represent the surface roughness. As illustrated in Figure 4, there are three rows of spheres stacked on a

Figure 3: Design feedback method to determine material parameters.

## Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits® is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

Figure 4: Cannonball model showing a stack of 14 uniform size spheres (left). Top and front views (right) shows the area (A<sub>flat</sub>) of base, height (H<sub>RMS</sub>) and radius of sphere (r).

Figure 5: Cannonball model with pyramid lattice structure. Five pyramids form a stacked lattice structure connecting the centers of all 14 spheres. Total height (H<sub>RMS</sub>) equals the stacked height of 2 pyramids plus the diameter (2r) of a single sphere.

square tile base. Nine spheres are on the first row, four spheres in the middle row, and one sphere on top.

Because the Cannonball model assumes the ratio of  $A_{\text{matte}}/A_{\text{flat}} = 1$ , and there are 14 spheres, Equation 4 can be simplified to:

$$K_{SR}(f) = 1 + 84 \left[ \frac{\left(\frac{(\pi r^2)}{A_{flat}}\right)}{\left(1 + \frac{\delta(f)}{r} + \frac{\delta^2(f)}{2r^2}\right)} \right]$$

Equation 5

Where:

$K_{SR}$  (f) = roughness correction factor, as a function of frequency, due to surface roughness based on the Cannonball model;

$r = sphere radius in meters; \delta(f) = skin-depth,$ as a function of frequency in meters; A<sub>flat</sub> = area of square tile base surrounding the 9 base spheres in sq. meters.

As shown in Figure 5, there are 5 squarebased pyramids connecting the centers of all 14 spheres forming a stacked lattice structure. A single pyramid, labeled ABCDE, is shown for reference.

Given that each side of the pyramid ABCDE = 2r, it can be shown that:

$$h = r\sqrt{2}$$

Since:

$$\begin{aligned} H_{RMS} &= 2r + 2h \\ &= 2r \left( 1 + \sqrt{2} \right) \end{aligned}$$

Then the radius of a single sphere is:

$$r = \frac{H_{RMS}}{2(1+\sqrt{2})}$$

And the area of the square flat base is:

$$A_{flat} = (6r)^2$$

## TAKE A VIRTUAL TEST DRIVE AND THE VICTORY LAP IS YOURS

VALOR PCB MANUFACTURING SOFTWARE | Move into the fast lane with a free test drive of the latest manufacturing technology from Valor®. Get hands-on access to our lean NPI design verification, process preparation, and production planning tools from virtually anywhere. Complete your trial lap, and you'll be ready to cross the finish line with higher efficiency, performance, and productivity throughout your PCB manufacturing processes. Go ahead, take the wheel at www.mentor.com/drive

You can approximate the RMS heights of the drum and matte sides by Equations 6 and 7:

$$H_{RMS\_drum} \approx \frac{R_{z\_drum}}{2\sqrt{3}}$$

Equation 6

Where: R<sub>z\_drum</sub> is the 10-point mean roughness in meters. If the data sheet reports average roughness, then R<sub>a drum</sub> is used instead.

$$H_{RMS\_matte} \approx \frac{R_{z\_matte}}{2\sqrt{3}}$$

Equation 7

Where:  $R_{z\_matte}$  is the 10-point mean roughness in meters.

#### **Practical Example**

To test the accuracy of the model, board parameters from Yuriy's Shlepnev's February 2014 article in *The PCB Design Magazine* [5] was used. Measured data was obtained from Simbeor software design examples courtesy of Simberian Inc. [9]. The extracted de-embedded generalized modal S-parameter (GMS) data was computed from 2-inch and 8-inch single-ended stripline traces. They were originally measured from the CMP-28 40 GHz High-Speed Channel Modeling Platform from Wild River Technology [15].

The CMP-28 Channel Modeling Platform, shown in Figure 6, is a powerful tool for development of high-speed systems up to 40 GHz, and is an excellent platform for model development and analysis. It contains a total of 27 microstrip and stripline interconnect structures. All are equipped with 2.92mm connectors to facilitate accurate measurements with a vector network analyzer (VNA).

The PCB was fabricated with Isola FR408HR material and reverse treated (RT) 1oz. foil. The dielectric constant (Dk) and dissipation factor (Df), at 10 GHz for FR408HR 3313 material, was obtained from Isola's isoStack web-based online design tool [10]. This tool is free, but you need to register to use it. An example is shown in Figure 7.

Figure 6: CMP-28 Modeling Platform from Wild River Technology. Photo credit Wild River Technology.

| 4        | isoStack  | Design name: CMP28             | Total number of cores: -1       |      |        |     | Nun    | Number of signal layers: 1    |      |        | Length | Frequency     |             |         |

|----------|-----------|--------------------------------|---------------------------------|------|--------|-----|--------|-------------------------------|------|--------|--------|---------------|-------------|---------|

| TSOSTACK |           | Date: Sat Mar 28 2015 12:08:48 | Total pressed thickness: 39.900 |      |        |     | Nun    | Number of reference planes: 3 |      |        |        | unit:<br>mils | 10GHz       |         |

|          | Thickness |                                | Ref.<br>plane                   | Zo   | Diff 2 | Tpd | Width  | Spacing                       | Fill | Weight | Dk     | Df            | Build       | Туре    |

| 1        | 1.400     |                                | true                            | na   | na     | na  | 5.000  | 10.000                        | 100  | 1      |        |               |             |         |

|          | 10.600    |                                |                                 |      |        |     |        |                               |      |        | 3.59   | 0.0095        | 3x3313-57.0 | FR408HF |

| 2        | 1.250     |                                | false                           | 49.0 | 98.0   | 161 | 10.380 | 10015.000                     | 0 5  | 1      |        |               |             |         |

|          | 12.000    |                                |                                 |      |        |     |        |                               |      |        | 3.65   | 0.0094        | 3x3313      | FR408HF |

| 3        | 1.250     | 19                             | true                            | na   | na     | na  | 5.000  | 10.000                        | 100  | 1      |        |               | 7.5         |         |

Figure 7: Example of Isola's isoStack online software used to determine dielectric thicknesses, Dk, Df and characteristic impedance for the CMP-28 board.

With our online system, getting quotes and placing orders is fast, simple and convenient. In fact every step of the process can be managed online–even payment! And our quality is guaranteed.

All you need to get started is to set up your account.

Create free account

Typical traces usually have a trapezoidal cross-section after etching due to etch factor. Since the tool does not handle trapezoidal cross-sections in the impedance calculation, an equivalent rectangular trace width was determined based on a 2:1 etch-factor (60 degree taper). The as designed nominal trace width of 11 mils, and a 1oz trace thickness of 1.25 mils per isoStack was used in the analysis.

The default foil used on FR408HR core laminates is MLS, Grade 3, controlled elongation RT foil. The roughness parameters were easily obtained from Oak-Mitsui [11]. Reviewing the data sheet, 1 oz. copper roughness parameters R<sub>z</sub> for drum and matte sides are 120 µin (3.175 µm) and 225 µin (5.715 µm) respectively. Because this is RT foil, the drum side is the treated side and bonded to the core laminate.

An oxide or micro-etch treatment is usually applied to the copper surfaces prior to final lamination. This provides enhanced adhesion to the prepreg material. CO-BRA BOND® [12] or MultiBond MP [13] are two examples of oxide alternative micro-etch treatments commonly used in the industry. Typically 50 µin (1.27 µm) of copper is removed when the treatment is completed. But depending on the board shop's process control, this can be 70-100 µin (1.78- $2.54 \mu m$ ) or higher.

The etch treatment creates a surface full of micro-voids which follows the underlying rough profile and allows the resin to squish in and fill the voids providing a good anchor. Because some of the copper is removed during the micro-etch treatment, we need to reduce the published roughness parameter of the matte

| Parameter                                                   | FR408HR                |

|-------------------------------------------------------------|------------------------|

| Dk Core/Prepreg                                             | 3.65/3.59 @10 GHz      |

| Df Core/Prepreg                                             | 0.0094/0.0095 @ 10 GHz |

| R <sub>z</sub> Drum side                                    | 3.175 μm               |

| R <sub>z</sub> Matte side before Micro-etch                 | 5.715 μm               |

| R <sub>z</sub> Matte side after 50 μin (1.27 μm) Micro-etch | 4.443 μm               |

| Trace Thickness, t                                          | 31.730 μm              |

| Trace Etch Factor                                           | 2:1 (60 deg taper)     |

| Trace Width, w                                              | 11 mils (279.20 μm)    |

| Core thickness, H1                                          | 12 mils (304.60 μm)    |

| Prepreg thickness, H2                                       | 10.6 mils (269.00 μm)  |

| GMS trace length                                            | 6 in (15.23 cm)        |

Table 1: CMP-28 test board parameters obtained from manufacturers' data sheets and design objective.

Figure 8: Example SEM photos of MLS RT foil. Left is the treated drum side and center is untreated matte side. SEM photo on the right is the matte side after etch treatment. (source Oak Mitsui)

side by nominal 50 μin (1.27 μm) for a new roughness of 175 µin (4.443 µm).

Figure 8 shows SEM photos of typical surfaces for MLS RT foil courtesy of Oak-mitsui. The left and center photos are the treated drum side and untreated matte side respectively. The right photo is a 5000x SEM photo of the matte side showing micro-voids after micro-etch treatment.

The data sheet and design parameters are summarized in Table 1. Respective Dk, Df, core, prepreg and trace thickness were obtained from the isoStack software, shown in Figure 7. Roughness parameters were obtained from the Oak-Mitsui data sheet. R, of the matte side after micro-etch treatment ( $R_z^2 = 4.443 \mu m$ ) was used to determine  $K_{sr matte}$ .